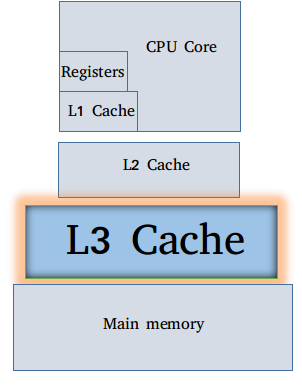

I am a Computer Engineering Master's student at Texas A\&M University. I aspire to specialize in VLSI systems and digital design to augment my knowledge in the developement of system on chip, the core hardware component that drives the growth of Internet of Things and meets the complex computational demands of today. I intend to pursue industrial research towards acheiving differentiated, optimized and reliable solutions in the field of integarted circuits to contribute towards emerging technological trends

I believe that the semiconductor industries have a huge role to play in the society. The hunger for faster, smaller and power effecient chips never recedes. With these requisites come more challenges in realizing a system on chip with emerging technology. I look forward to address these in my research career. With the right background in understanding its importance to learning the current limitations in the field of VLSI and computer architecture, I am committed to learn and work towards a better technological tomorrow.